Электроника МС 8002

Адаптер «Электроника МС 8002» организует скоростную межпроцессорную дуплексную связь в многомашинных вычислительных комплексах на базе мини-ЭВМ, имеющих канал типа «Общая шина» (СМ ЭВМ), и «Электроника 100-25», «Электроника 79» для повышения производительности и надежности.

рис. 1

Один из подходов к повышению производительности, живучести и надежности систем [1, 2] — использование многомашинных вычислительных комплексов.

Пример — комплекс в гибкой производственной системе, на котором организована централизованная база данных для хранения технологических карт, загружаемых на конкретный исполнительный элемент системы. Второй пример — региональный центр системы бронирования и продажи авиабилетов, обслуживающий аэропорт областного центра, где требуются повышенные надежность и быстродействие, но установка «большой» ЭВМ экономически невыгодна. Организация эффективной работы многомашинных вычислительных комплексов невозможна без применения в них средств скоростной межпроцессорной связи.

Описание адаптера «Электроника МС8002

Адаптер «Электроника МС 8002» (рис. 1) подключается к каналу ЭВМ «Общая шина» на правах контроллера внешнего устройства.

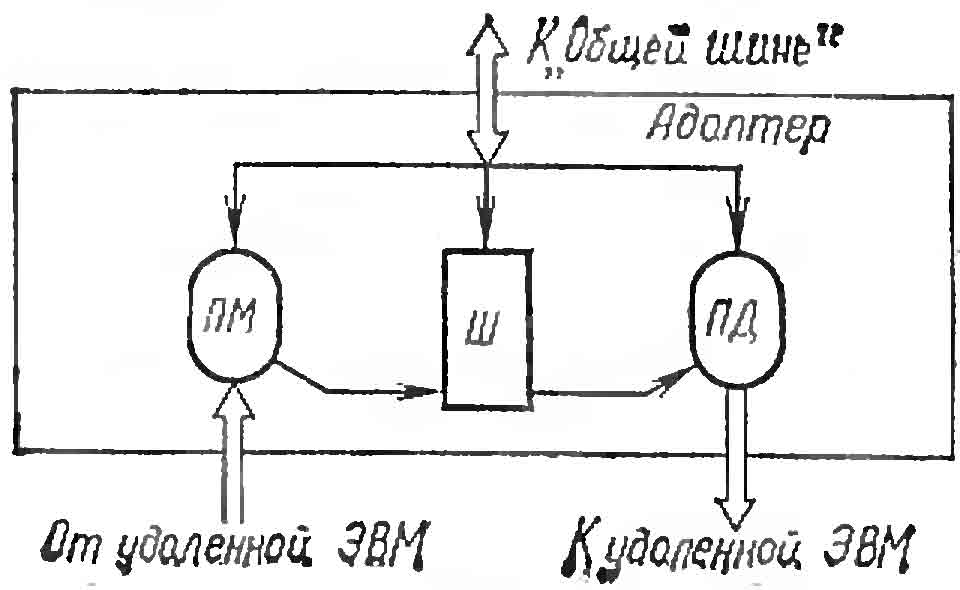

Рис. 2. Структурная схема адаптера «Электроника МС 8002»:

ПМ — блок приемника; ПД — блок передатчика; Ш — блок тестового шлейфа

Адаптер содержит три практически независимых блока (рис. 2): блок приемника, блок передатчика, блок тестового шлейфа. Управление каждым блоком независимое и соответствует традиционным архитектурным принципам, но набор выполняемых функций оптимизирован для скоростного обмена и упрощения отладки протокольных программ.

Блоком приемника управляют через регистры состояния и управления (РСУПМ), адреса памяти (РАППМ), счета слов (РССПМ), встроенного таймера (РТПМ), ошибок (РОШПМ), данных (РДПМ).

В регистре РСУПМ могут быть заданы пять операций: ввод, фиктивный ввод, ввод без таймерного контроля, фиктивный ввод без таймерного контроля, отсчет времени. При выполнении «ввода» данные, поступающие от удаленной ЭВМ, вводятся (и размещаются) в оперативную память, подсчитывается контрольный интервал времени, величина которого задана в 16-разрядном регистре таймера РТПМ, а вес одного разряда РТПМ задан в регистре РСУПМ.

Начальный адрес ОЗУ и длина вводимого массива задаются в регистрах РАППМ и РССПМ соответственно. При фиктивном вводе принимаемая информация не записывается в ОЗУ подключенной ЭВМ.

Таймерный контроль может быть выключен заданием разновидности операции ввода.

Ввод можно завершить по исчерпанию области памяти, отведенной для приема, при поступлении сигнала конца массива от удаленной ЭВМ или по ошибке. При завершении ввода процессор прерывается по отдельному для приемника вектору.

Ошибки приема фиксируются. В регистре РОШПМ предусмотрено позиционное кодирование срабатывания таймерного контроля, неотвечающей памяти, нарушения последовательности сигналов синхронизации, нарушения четности на интерфейсе с удаленной ЭВМ.

Блок передатчика имеет для программного управления регистры: состояния и управления (РСУПД), адреса памяти (РАППД), встроенного таймера (РТПД), ошибок (РОШПД), данных (РДПД). Блоку передатчика можно задать пять операций: вывод, фиктивный вывод, вывод без таймерного контроля, фиктивный вывод без таймерного контроля, отсчет времени. При выполнении «вывода» данные из указанной области оперативной памяти выводятся в интерфейс удаленной ЭВМ, ведется подсчет контрольного интервала времени, величина которого задана в регистре РТПД, а вес одного разряда РТПД — в регистре РСУПД.

Начальный адрес ОЗУ и длина выводимого массива данных задаются в регистрах РАППД и РССПД соответственно. Таймерный контроль можно выключить, задав разновидность операции вывода. При фиктивном выводе в интерфейс удаленной ЭВМ выводится информация не из оперативной памяти, а из регистра данных, и обращение в ОЗУ не производится. Вывод может быть завершен либо по окончании передачи всех указанных в регистре РССПД данных, либо по истечении контрольного интервала времени, либо при обнаружении ошибок. При завершении операции процессор прерывается по отдельному для передатчика вектору.

Ошибки передачи фиксируются. В регистре РОШПД предусмотрено позиционное кодирование срабатывания таймерного контроля, неотвечаюшей памяти, нарушения последовательности сигналов синхронизации в интерфейсе с удаленной ЭВМ.

Операции фиктивного ввода и вывода предусмотрены для тестирования и реализации разнообразных протоколов межмашинного взаимодействия. Совмещение таймерного отсчета позволяет реализовать контроль по времени в пределах программы-драйвера без обращения к общесистемной таймерной службе. Так как установка контрольного интервала времени делается во многих протоколах при задании каждой операции обмена, наличие встроенных таймеров приводит к снижению затрат времени процессора на таймерные операции. Например, при средней длине массива в 1 Кбайт и темпе обмена в 1 Мбайт/с обращения процессора к таймерной службе должны были бы следовать с интервалом в 1000 мкс. Это обусловило бы значительную часть затрат производительности процессора. Вес одного разряда регистров таймеров можно программно указать равным 10 мкс или 1 мс. Это даст возможность назначать длину контрольного интервала от 10 мкс или 1 мс до 64 с с шагом 1 мс.

Блоком тестового шлейфа управляют через программно-доступные регистры состояния и управления (РСУТШ) и данных (РДТШ). При работе в режимах тестовых проверок и отладке программ можно задать четыре разновидности работы тестового шлейфа: режим полной операции, режим одиночных слов, режим группы из К-слов и режим имитации ошибок.

В режиме полной операции все управляющие сигналы и сигналы данных транслируются с выхода передатчика на вход приемника без искажений. В режиме одиночных слов передача очередного 16-разрядного слова с выхода передатчика на вход приемника происходит по команде процессора. В режиме группы из К-слов по одной команде процессора с выхода передатчика на вход приемника передаются только К-слова, причем число К задается записью в регистр РДТШ В режиме имитации ошибок тестовый шлейф работает, как в режиме одиночных слов, с тем отличием, что в приемник поступают из передатчика только контрольные разряды, а сами данные принимаются в приемник из регистра РДТШ.

Все эти предусмотренные функции упрощают отладку программ протоколов связи, позволяют проверять и сами схемы обнаружения ошибок. Реализация управления тестовым шлейфом с помощью отдельных регистров создает удобства для написания отдельных программ имитации обмена и позволяет не проводить никаких изменений в рабочих программах при отладке с использованием имитационных программ. Такая отладка программ, реально взаимодействующих с аппаратурой, значительно уменьшает продолжительность отладки в снимает психологическую напряженность в работе программиста, поскольку даст инструмент детального наблюдения и точ ного контроля работы отлаживаемой программы.

Адаптер «Электроника МС 8002» конструктивно выполнен в виде комплектного блока, который встраивается в стойку СМ ЭВМ согласно стандартам СЭВ 834—78. Современная элементная база адаптера размещена на 15 платах размером 135х240 мм. Канал типа «Общая шина» подсоединяется к адаптеру с помощью наборных разъемов типа РШЗП (ЗШ2Т), установленных на задней стенке устройства. Кабели межмашинного интерфейса подсоединяются к адаптеру через разъемы с коаксиальными контактными парами, установленные на ТЭЗах физического согласования.

В комплект адаптера входит панель для автономной настройки, однако она может использоваться и при работе устройства в составе комплекса. Индикаторы панели упрощают отладку программного обеспечения. Клавиатура панели служит для изменения глубины буферной памяти приемника и передатчика. Панель можно навесить вместо передней стенки корпуса адаптера или на переднюю стенку (см. рис. 2).

Технические характеристики адаптера «Электроника МС 8002»

Со стороны асинхронных каналов вводи и вывода:

Режим работы - Дуплексный

Разрядность передаваемых данных - 16 бит

Защита от ошибок - Контроль четности для каждых четырех разрядов данных

Максимальная скорость обмена – 1 200 000 слов/с

Со стороны канала «Общая шина»:

Режим работы - Непосредственный доступ к памяти с раздельным управлением для ввода и вывода

Разрядность передаваемых данных -16 бит

Максимальная длина массива - 65 536 слов

Максимальная задержка ретрансляции данных:

Из асинхронного канала вывода в «Общую шину» - не более 650 нм

Из «Общей шины» в асинхронный канал ввода - не более 800 нс

Режим работы тестового шлейфа

Полная операция:

Одно слово

Группа слов

Имитация ошибок

Габариты 485х485х310 мм

Потребляемая мощность не более 350 ВА

Напряжение 220 В

Частота 50 Гц

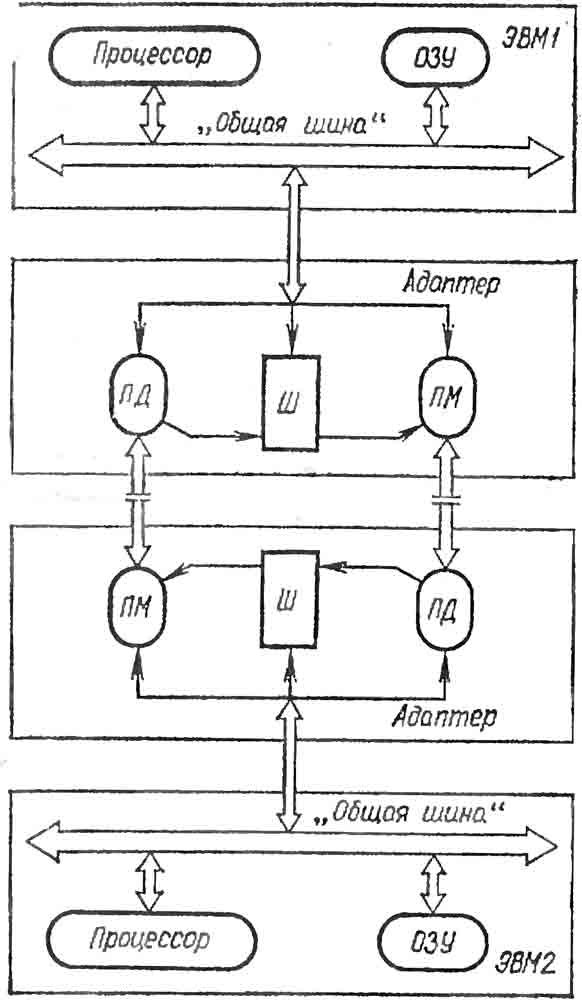

Организация дуплексной связи между ЭВМ с помощью адаптеров «Электроника 8002»

Соединяемые ЭВМ обмениваются данными в режиме прямого доступа в память соединяемых ЭВМ. Обменом управляют с помощью прерывания и программного доступа к управляющим регистрам. Связь ЭВМ строится по конфигурации «точка-точка» с установкой по одному адаптеру на каждую из соединяемых ЭВМ при длине кабелей связи до 25 м (рис. 3). Скорость обмена через адаптер существенно зависит от быстродействия ОЗУ ЭВМ и при цикле ОЗУ, равном 650 нс, достигает 1 Мбайт/с в каждом направлении при одновременных потоках данных (в дуплексном режиме).

Рис. 3. Структурная схема организации дуплексной связи двух ЭВМ с помощью адаптеров «Электроника МС 8002». Обозначения те же, что и на рис. 2

Два адаптера, подключенных к разным ЭВМ, соединяются между собой с помощью набора из 25 параллельных линий в каждом направлении. В состав линий входят 16 линий данных Д0...Д15; 4 линии контроля данных КО...КЗ; 3 линии’ синхронизации: ГОТОВ, ПРОДОЛЖИТЬ, РАЗЪЕДИНИТЬ; одна линия указателя имитационного шлейфа — ШИ; одна линия программного сброса канала — ПСК. Сигналы на линиях данных и контроля, линиях ШИ и ПСК — потенциальные, а на линиях синхронизации — импульсные. Логика синхронизации — старт-стопная.

Одновременно с каждыми 16 разрядами данных, сопровождаемыми контрольными разрядами, подается сигнал ГОТОВ, а после приема этих данных — сигнал ПРОДОЛЖИТЬ. После передачи последнего слова массива и получения сигнала ПРОДОЛЖИТЬ выдается сигнал РАЗЪЕДИНИТЬ, означающий для приемника окончание массива в передатчике.

Максимальная скорость передачи сигналов по такому интерфейсу ограничена суммой двух времен распространения по кабелю, двух длительностей импульсных сигналов синхронизации (по 50 нс каждый) и двух времен реакции адаптеров. Время распространения по кабелю длиной 25 м составляет 25х2х5 = 250 нс. Если предположить мгновенную реакцию адаптеров, то общая сумма будет равна 2х50+250 = 350 нс на передачу каждых 16 разрядов данных.

Реально при работе адаптеров в контрольно-измерительном режиме «фиктивный ввод—фиктивный вывод», в котором игнорируется быстродействие памяти процессора, получена скорость порядка 2,2 Мбайт/с, т. е. сумма двух времен реакции — 800 нс.

Сигнал программного сброса ПСК, принимаемый из межмашинного интерфейса в адаптер, означает, что в передатчике ЭВМ-партнера программно установлен нуль. Этот сигнал упрощает и ускоряет выполнение повторного старта обмена.

Сигнал на линии имитационного шлейфа указывает о переводе обоих наборов линий для передачи и приема в состояние имитационного шлейфа. Набор линий для приема данных соединяется в оконечных ТЭЗах адаптера с набором линий для передачи данных. Состояние линии ШИ задастся программно, записью в соответствующий разряд регистра РСУПД в «собственном» адаптере и индицируется соответствующим разрядом в регистре РСУПМ адаптера удаленной ЭВМ.

Таким образом, из одной ЭВМ можно задать тестирование «собственного» адаптера, кабелей связи и ТЭЗов физического сопряжения в адаптере, подключенном к удаленной ЭВМ Такая возможность вместе с введением блока локального тестового шлейфа повышает надежность и эксплуатационные показатели комплексов из ЭВМ.

Каждая линия межмашинного интерфейса реализуется в виде двух коаксиальных кабелей (при передаче парафазным сигналом) с волновым сопротивлением 50 Ом, диаметром оплетки 1,0 мм. Таким образом, между машинами укладывается 100 коаксиальных кабелей в виде двух жгутов (диаметр каждого 25 мм). Согласующие элементы, непосредственно работающие на кабель. — микросхемы К500ПУ124 и К500ПУ125.

Для повышения быстродействия адаптера приняты специальные структурные решения: установлен в каждом направлении обмена буферной памяти объемом 16х16 бит с дисциплиной FIFO, введена пакетная передача данных на участке адаптер—ОЗУ.

Буферная память реализована на элементах КР1802ИР1 и работает со скоростью записи-чтения 5 Мслов/с. В блоке приемника разгружать буферную память можно в двух режимах: прямого доступа к ОЗУ подключенной ЭВМ и программного чтения выхода памяти с помощью обращения процессора к регистру данных приемника РДПМ. В блоке передатчика буферная память загружается также в двух режимах: прямого доступа и программной записи с помощью обращения к регистру данных передатчика РДПД.

Пакетирование передачи на участке адаптер—ОЗУ (при работе в режиме прямого доступа) заключается в следующем. При вводе данных в ОЗУ подключенной машины после накопления в буферной памяти хотя бы одного слова адаптер посылает запрос на захват канала «Общая шина». При предоставлении адаптеру доступа к каналу можно передавать не одно, а несколько записанных в буфер слов за одну процедуру доступа. При пакетированной передаче контролируется наличие требований прямого доступа от других устройств, подключенных к каналу, например дисковых накопителей. По такому требованию канал освобождается, а если требований нет, то данные передаются в ОЗУ подключенной ЭВМ до полной разгрузки буферной памяти адаптера. Аналогично используется память в передатчике при загрузке данных из ОЗУ подключенной ЭВМ в буферную память передатчика.

ЛИТЕРАТУРА

1. Вейцман К. Распределенные системы мини- и микроЭВМ/Пер. с англ.; Под ред. Г. П. Васильева. — М.: Финансы и статистика, 1980.

2. Каляев А. В. Принципы организации многопроцессорных систем сверхвысокой производительности. — Микропроцессорные средства и системы, 1984, № 2, с. 31—35.

3. Пролейко В. М. Микропроцессорные средства вычислительной техники и их применение. — Микропроцессорные средства и системы, 1984, № 1, с. 11 —16.

УДК 681.324

Ю. Н. Знаменский, В. В. Карев, Л. Я. Крушевский, А. В. Маслов, С. П. Поликарпочкин

Статья поступила 1 декабря 1984 г. |